# DESIGN OF DIFFERENT DIGITAL CIRCUITS USING SINGLE ELECTRON DEVICES

BananiTalukdar<sup>1</sup>, Dr.P.C.Pradhan<sup>2</sup> and Amit Agarwal<sup>3</sup>

#### **ABSTRACT**

Single Electron transistor (SET) is foreseen as an excellently growing technology. The aim of this paper is to present in short the fundamentals of SET as well as to realize its application in the design of single electron device based novel digital logic circuits with the help of a Monte Carlo based simulator. A Single Electron Transistors (SET) is characterized by two most substantial determinants. One is very low power dissipation while the other is its small stature that makes it a favorable suitor for the future generation of very high level integration. With the utilization of SET, technology is moving past CMOS age resulting in power efficient, high integrity, handy and high speed devices. Conducting a check on the transport of single electrons is one of the most stirring aspects of SET technologies. Apparently, Monte Carlo technique is in vogue in terms of simulating SED based circuits. Hence, a MC based tool called SIMON 2.0 is exercised upon for the design and simulation of these digital logic circuits. Further, an efficient functioning of the logic circuits such as multiplexers, decoders, adders and converters are illustrated and established by means of circuit simulation using SIMON 2.0 simulator.

#### KEYWORDS

Coulomb Blockade, Single Electron Transistor (SET), tunnelling, Quantum Dot, Tunnelling Rate, CMOS, multiplexers, decoders, adders, Binary to Gray code converter, Gray to Binary Code converter, SIMON.

## 1. Introduction

One of the extraordinary creations of the 20<sup>th</sup> century is the semiconductor transistor. The last decade has seen a startling shrinkage in the feature size of MOS based circuits and an upsurge in the number of transistors. CMOS technology had a supremacy over the decades as bestowed by Moore's Law. As a result, the integration scale will be confined since power consumption will rise above the cooling limit [1]. The SED operation relies on a unique phenomenon called Coulomb Blockade which occurs in nanostructure and Gorter observed and studied this at a very low supply voltage [2]. The basic element of a single electron transistor is the tunnel junction [3]. As opposed to a MOSFET, the current conduction in a SET is regulated by the quantum mechanical tunnelling of electrons through the tunnel barrier. SET has immense potential for the evolution of future pint sized circuits as work has already been carried out for the evolution of set logic gate families [4], adders [5],[6], PLAs [7] etc. In this paper, Section II presents a brief description of MOSFET [8] and scaling limits [9]. In Section III, a review on SET is provided. Section IV deals with Coulomb Blockade [10] and orthodox theory whereas Section V provides an insight into the design and simulation results of different digital circuits utilizing MC [11] based simulator SIMON 2.0 [12].

DOI:10.5121/msej.2016.3102

<sup>&</sup>lt;sup>1</sup>Department of Electronics & Communication Engineering, Sikkim Manipal Institute of Technology, Majitar, East Sikkim.

<sup>&</sup>lt;sup>2</sup>Department of Electronics & Communication Engineering, Sikkim Manipal Institute of Technology, Majitar, East Sikkim.

<sup>&</sup>lt;sup>3</sup>Department of Electronics & Communication Engineering, Sikkim Manipal Institute of Technology, Majitar, East Sikkim.

## 2. MOSFET

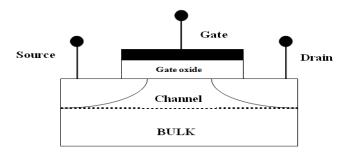

MOSFET became the chief microelectronic device because it proved to be an essential building block of VLSI circuits. A MOSFET can be defined as a device consisting of four terminals i.e. drain, source, gate and bulk (see Figure 1).

Figure 1: Generic MOSFET [13]

The MOSFET is primarily used as a switch in digital circuits. Its working can be demonstrated in the manner that the source and drain are two ends of the switch and the gate controls the turning ON & OFF of the channel. The gate terminal uses an electric field to control the conduction through the channel. The gate is insulated from the channel by a delicate layer of silicon dioxide. MOSFETs can be classified into types: nMOS and pMOS. They basically differ in the voltages that turn on the switch. Either type of the MOSFET is dependent on the element used to dope the silicon. In an nMOS transistor, an n-type material like Phosphorus is utilized to heavily dope the drain and source, while a p-type material is used to lightly dope the channel. On the other hand, in a pMOS transistor the drain and source are p-type and the bulk and channel are n- type. The MOSFET also has the ability to segregate the input from the output (gate to source or drain) which is an inclusion to its potential to implement logic. This ability of the MOSFET entitlesit to illustrate gain. Since a signal passes through a large number of transistors presuming that a little voltage is obscured at each transistor, then eventually the signal will deteriorate. The MOSFETs can be utilized to incorporate further intricate layout, which is another crucial feature of MOSFETs. The most common logic family, CMOS (Complementary metal-oxide semiconductor), adopts complimentary nMOS and pMOS transistors to frame logic gates such as inverters and NAND gates. Advances in the field of electronics have chaperoned to further retrench the size of the MOSFETs applied in integrated circuits. The decrease in size of the transistors also makes each one of them swift and they dissipate less power. The transistors become faster because there is a drop in the capacitance and boost in current. The increase in current can be visualized from the current flow equation for a transistor, when the gate voltage is at its highest value [13]. The current through the channel is given by the equation (A first order approximation):

$$I_D = \mu C_{OX} W/2L (V_{GS}-V_{th})^2$$

(1.1)

The above equation illustrates how different criterions of the MOSFET influence its behavior. An upsurge in power consumption mainly through leakage currents, decreased tolerance for process variation and roaring costs are some of the aspects that affect the MOSFET scaling (decrease in size). Merely shrinking the size of the gate length and width will not lead to proper scaling but also demands a shortening of all the other dimensions; covering the gate/source and gate/drain alignment and the oxide thickness and depletion layer widths. When we scale down the depletion layer width it also indicates the need to scale down the doping density. There are two types of scaling listed below which are frequently used. One is constant field scaling and the other is constant voltage scaling. When the channel length of a MOSFET device is of same order

of magnitude as the depletion layer widths of the source and drain junction, the MOSFET device is considered to be short [14]. Assuming the channel length to be L; when the channel length L is reduced, the operation speed as well as the number of components per chip increases. In lieu of increasing the operating speed and the number of components, the problem of short- channel effect arises. The short channel effect is marked by two physical phenomena. They are as under: First, the shortcomings of the electron drift characteristics in the channel. Second, the shortening of the channel length results in the alteration of the threshold voltage.

## 3.SINGLE ELECTRON TRANSISTOR

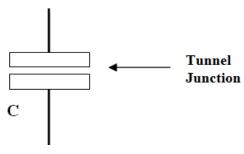

We can characterize a Single electron transistor as a three-terminal, nano-electronic, tunnel junction device which utilizes a capacitively-coupled input voltage to modulate a drain-source current aiding as the amplifier output [15]. The tunnel junction is the chief element of a single electron transistor. The electric charge passes through the tunnel junction as multiples of e, given tunnelling is a discrete process [16].

Figure 2: Tunnel Junction [17]

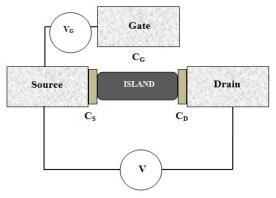

Further, when two tunnel junctions are laid down in series configuration, the fundamental construction of a single electron device can be obtained. The piece of conductor sandwiched between the two tunnel junctions is generally recognized as the island. It may also be called grain or a dot.

Figure 3: Structure of SET [18]

In Simple words, we can deliberate SET as a circuit that subsist of islands which are promptly connected with tunnel junctions and capacitors in conjunction with ideal voltage sources which control the circuits. In these devices, since  $k_BT << E_{cmin}$ ; the operating temperature (T) is diminished. Here  $E_{cmin}$  is the minimum charging energy. The minimum charging energy is also identical to the energy level spacing of the island[19]. In the above equation  $k_B$  is the Boltzmann constant. The minimum charging energy can be written as:

$$E_c = e^2 / 2C_{\Sigma} \tag{1.2}$$

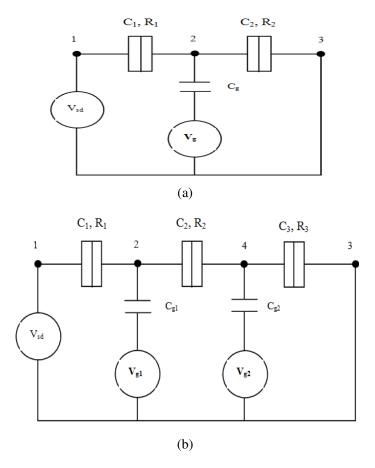

$C_{\Sigma}$  is the total capacitance of the island. In other words, we can deliberate that the junction capacitance should be sufficiently small so as to reflect that the charging energy is higher than the thermal energy. Tunnel junctions, capacitances and voltage sources devise single electron circuits. Because of the stochastic nature of the electron tunnelling event, a tunnelling electron can be characterized as a discrete charge. We can note that in the Figure 4, the node 1 serves as the source electrode, node 2 & 4 behave as the island while node 3 again serves as the drain electrode. The regions between the nodes are the tunnel junctions which are defined by tunnel capacitance, C and tunnel resistance, R. Just as the bias voltage is zero the Fermi levels of both source and drain are in equilibrium, and it remains in equilibrium till there is some exertion of the bias voltage.

Figure 4 :( a) Equivalent circuit of SET consisting of tunnel and non-tunnel junctions with ideal voltage sources, (b) SET with double islands [17, 19].

There will be independent tunneling of an electron through the tunnel junctions from source to drain over the dot when an empty state is present at the energy level of the island that lies between the Fermi levels of the electrodes.

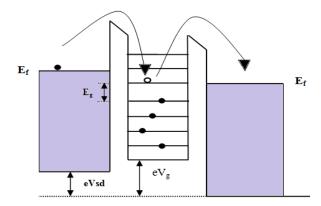

Figure 5: Schematic band diagram of Single electron transistor [19].

The electrostatic potential of the island is transformed by the electron tunnelling. The electron tunnelling also recasts the charge distribution in the circuit. As we modify the gate voltage various mannerisms of the circuit also changes them being the shifting of the energy levels, regulation on the addition and removal of electrons and turn on & off operations of the device. As opposed to a MOSFET, the current conduction in a SET is regulated by the quantum mechanical tunnelling of electrons through the tunnel barrier. A tunnel junction consists of two pieces of metal supported by a very thin (about 1 nm) insulator. Tunnelling through the insulator is the sole means for an electron to move from one metal electrode to the other [20]. Under some certain assumptions, since only one electron can travel from one terminal to another at a time, the device is commonly known as a SED (Single electron device). Charge transport is of discrete nature in a SED and is continuous in case of a MOSFET.

## 4. COULOMB BLOCKADE

Let us try to understand this phenomenon of coulomb blockade with the help of a small example. Let us assume a small spherical electro neutral conductor having capacitance C. The electron addition energy  $(E_A)$  is the amount of work that has to be done in order to add an extra electron to the spherical electro neutral conductor. Therefore,  $E_A$  can be written as:

$$E_A = E_C + E_K \approx E_C \approx e^2 / C \tag{1.3}$$

Where  $E_C$  is the charging energy and  $E_K$  is the quantum kinetic energy respectively. Normally when the feature size is found to be more than 1nm; the quantum kinetic energy,  $E_K$  is omitted. Subsequently, the electrons in a single electron system require a minimum energy to tunnel through the barrier. When the applied external biases are unable to provide this energy, an electron cannot tunnel through. The device then goes into an OFF state. Such a condition is the Coulomb Blockade. The minimum energy required by the electrons to tunnel through can also be acquired from the existing thermal energy sources. Hence, to avoid the tunnelling of electron owing to the thermionic emission, the charging energy of the island capacitance has to be substantially higher than the existing thermal energy,  $K_BT$ . This can be written as:

$$(e^2/C)/k_BT > \beta$$

(1.4)

T represents the room temperature whereas  $K_B$  is the Boltzmann's constant. The sum of all the device capacitance gives the total capacitance of the QD. This can be written as:

$$C_T = C_G + C_D + C_S$$

(1.5)

It is also observed that the SET device operable at room temperature requires exceptionally demanding nanofabrication technology. A simple but productive orthodox theory has played an exclusive guiding role throughout the history of Single electronics. Kulik and Shekhter [21] had established the theory for a particular case study which was expanded for general systems by Averin and Likharev [22, 23]. This theory developed by Kulik and Shekhter, is based on the following assumptions. The electron energy spectrum is continuous, within the island. This particular assumption is valid for  $E_k << k_b T$ . Here Ek and  $E_c$  define the electron kinetic energy and charging energy, respectively [24]. Analogizing with other time scales, the time taken by the tunneling of electrons over the barrier  $(\tau_t)$  is deemed negligible. For a SED of factual interest the assumption that  $\tau_t$  must be  $10^{-15}$  seconds holds true. It has to be noted that coherent quantum processes involving various concurrent tunneling events or cotunneling have been defied. This particular assumption holds true only under the event where electrons are effectively confined in the island. When tunnel resistances are larger than the fundamental resistance  $R_q$ , the confinement of the electron states within the islands can be ensured. The fundamental resistance is given as under:

$$R > R_0 = h/e^2 = 25.813\Omega$$

(1.6)

The QD (quantum dot) is connected to the source and drain electrodes through tunnel barriers. The gate electrode steers the potential in the Quantum Dot which is also capacitively coupled to the Quantum Dot [25]. The gate voltage (Coulomb Oscillations) systematically modulates the current through the dot. The number of electrons is fixed when the current is zero. To limit the electrons in the Quantum Dot, the tunnel junction resistances must be greater than the quantum resistance (25.8 k $\Omega$ ). The rates of all the possible tunnel events has to be resolved in order to mirror the tunneling of electron from island to island in a single electron circuit. The circuit's free energy changes as a result of a tunnel event. This change in the free energy decides the rate at which a tunnel event would take place. The difference between the electrostatic energy stored and the work done by the voltage sources of the circuit; denoted by U and W respectively can be expressed as:

$$F=U-W (1.7)$$

The tunneling rate of a tunnel event can be expressed as:

$$\Gamma = \frac{\Delta F}{e^2 R_T (1 - e^{-\frac{\Delta F}{kT}})} \tag{1.8}$$

$\Delta F$  here represents the change in the free energy as a result of the tunnel event, the tunnel junction resistance over which the electron is conducted is given by RT; kT is the thermal energy (k being the Boltzmann's constant and T is the temperature.

## 5. SIMON

A Monte Carlo based simulator for single electron circuits and devices is available and is named "SIMON". This simulator helps to report many of the design catechisms that arise. Basic features like graphical user interface and graphical circuit editor caters for and easy and error free handling of the simulator [26]. Circuit units like the tunnel junctions, capacitors, voltage sources and measuring devices for voltage, current and charge can be connected subjectively and all it requires is a mere mouse click. A few new features have been appended in the software which are: Stability plot, normal resistors, current sources, energy dependent density of states, and support for superconducting tunnel junctions, interactive single step mode, and Linux version without need for third party tools. We can simulate co-tunnelling with a simple Monte Carlo method. Most importantly, with SIMON we can confer about the crucial random problems like

background charge coupled with some possible solutions. We are considering single electron tunnel circuits which consists of islands connected randomly to tunnel junctions and capacitors and are impelled by voltage sources. The internal resistance of the voltage source is zero and hence it is deemed ideal. This work presents the design, simulation and analysis various digital circuits using SET. SIMON 2.0 is used to simulate the logic operation of gates, multiplexers, decoders, adders and converters.

## 5.1 Inverter

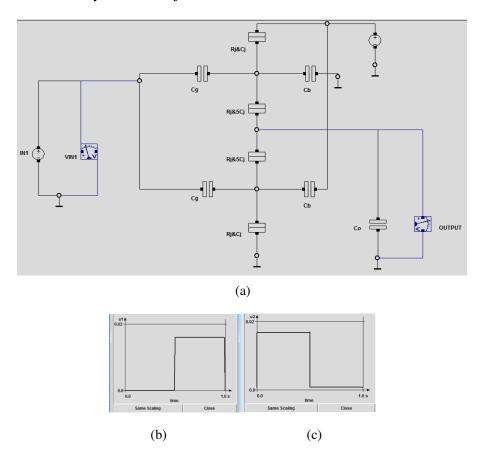

The basic building block of SET technology is the inverter that has noticeable alikeness to standard CMOS logic. The single electron inverter is shown in Figure 6, where five islands are hitched by four tunnel junctions.

Figure 6: (a)Single electron device based Inverter (b) Input waveform of Inverter (c) Simulation results of Inverter

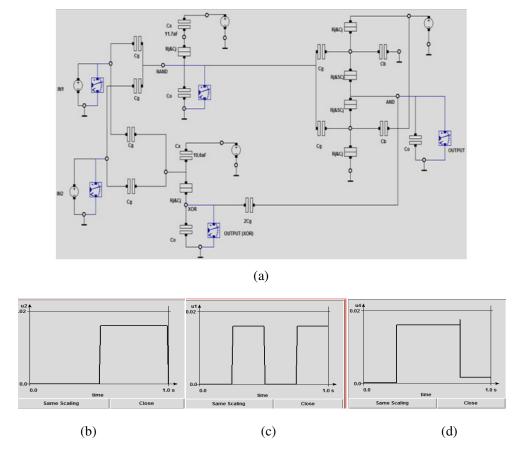

## 5.2 Xor Gate

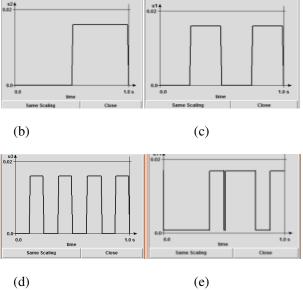

The XOR gate also marked as Exclusive ORgate or an inequality detector is a digital logic gate that devices an exclusive or operation. This means that a true output follows up if one, and only one, of the inputs to the gate are true. If either inputs are false or both are true, a false output follows. The Single electron XOR gate is shown in Figure 7 below.

Figure 7: (a) Single electron device based XOR Gate (b) Input 'A' of XOR Gate (c) Input 'B' of XOR Gate (d)Simulation results of XOR Gate

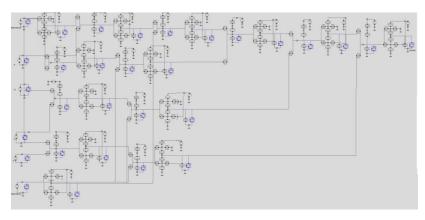

# 5.3 2:1 Multiplexer

A Multiplexer is a combinational logic circuit. It can also be written as MUX or MPX. Depending on the application of a control signal, it can be used to switch one of several input lines through to a single common output line. The SET based 2 to 1 line multiplexer is shown in the figure below.

(a)

Figure 8: (a)Single electron device based 2:1 Multiplexer (b) Input waveform 'A0' of 2:1 Multiplexer (c) Input waveform 'A1' of 2:1 Multiplexer (d) Select Line, 'S' (e) Simulation results of 2:1 Multiplexer

## 5.4 4:1 Multiplexer

A logic circuit that picks one data line from amidst many is a multiplexer. They are often referred to as data selectors. A 4:1 line multiplexer illustrates how it channels out information from multiple data lines to one data line. The circuit for SET based 4:1 line multiplexer is shown in the figure below.

Figure 9: (a) Single electron device based 4:1 Multiplexer(b) Select line, S0 (c) Select line, S1(d) Simulation results of 4:1 Multiplexer.

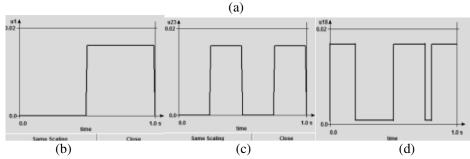

## 5.5 2:4 Decoder

A decoder is one of the multiple input-output logic that allows us to obtain coded outputs derived from the coded inputs. Decoding is particularly essential in applications as multiplexing, memory address decoding.

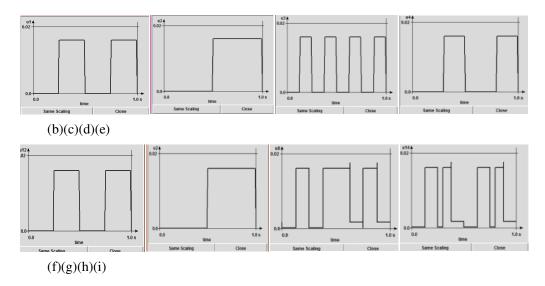

Figure 10:(a) Single electron device based 2:4 Decoder. Simulation results of 2:4 Decoder:(b) Input waveform 'X' (c) Input waveform 'Y' (d) Output waveform O0 (e) Output waveform O1 (f) Output waveform O2 (g) Output waveform O3

## 5.6 Parallel Adder

Another combinational circuit is the Parallel Adder which is not clocked or doesn't have a memory of its own. It does not have a feedback. It adds every bit position of the operands at the same time. Therefore, the number of bits to be added reflects the number of bit adders required. The Parallel Adder designed using SIMON 2.0 is as follows.

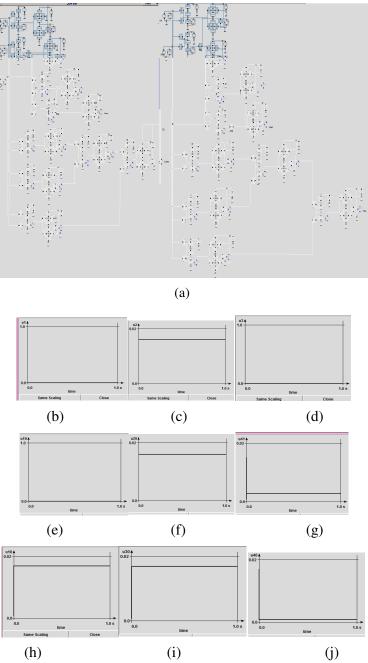

Figure 11: (a) Single electron device based Parallel Adder.Simulation results of Parallel Adder:(b) Input waveform A0 (c)Input waveform B0 (d) Input waveform C0 (e) Input waveform A1 (f) Input waveform B1 (g) Input waveform C1 (h) Sum Output waveform of first Full Adder, S0 (i) Sum Output waveform of second Full Adder, S1 (j) Output waveform Cout of Parallel Adder

## 5.7 Look Ahead Carry Adder

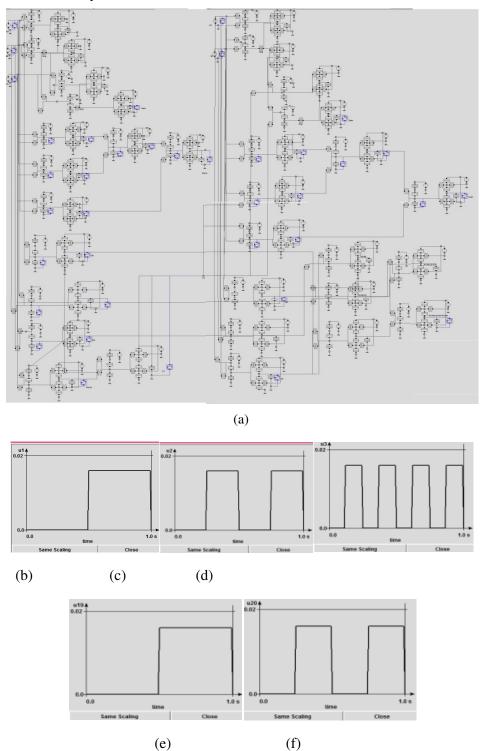

Another type of adder used in digital logic is a look ahead carry adder also known as the fast adder. As opposed to a slower ripple carry adder, the speed of operation is improved by decreasing the amount of time needed to determine the carry bits. The single electron device based look ahead carry adder is shown below.

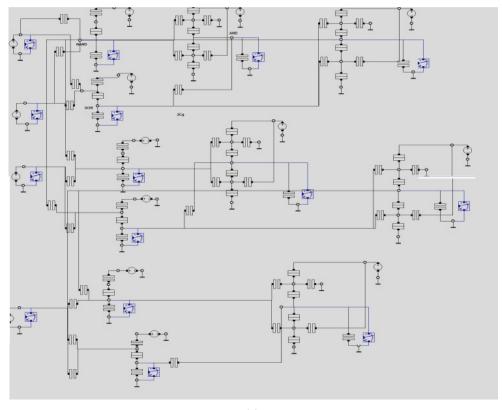

Figure 12: (a) Single electron device based Look Ahead Carry Adder. Simulation results of Look Ahead Carry Adder: (b) Input waveform A0 (c) Input waveform B0 (d) Input waveform C0 (e) Input waveform A1 (f) Input waveform B1 (g) Output waveform S0 (h) Output waveform S1 (i) Output waveform C1(j) Output waveform C2 of Look ahead carry adder.

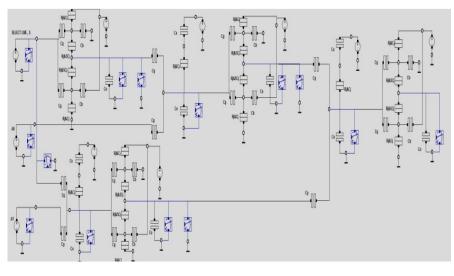

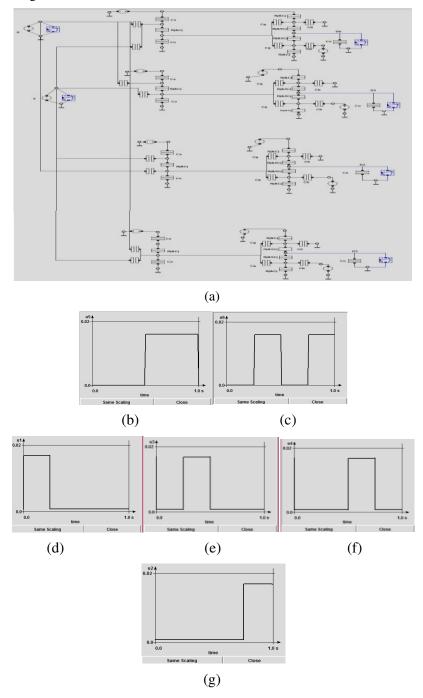

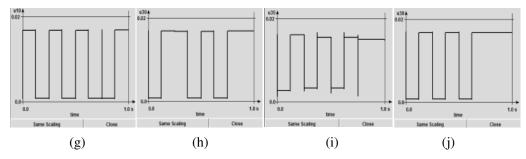

## **5.8 Binary to Gray Code Converter**

The text or data that the computers or other devices bear is staged by a binary code. The text or data is personified as a sequence of zeroes and ones. Gray codes are essential as they find a plenty of application in analog as well as digital converters. Two adjacent code numbers can be distinguished from each other by just one bit. The single electron device based binary to gray code converter is shown in the figure below.

(a)

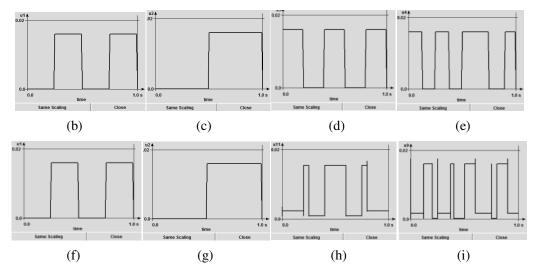

Figure 13: (a) Single electron device based Binary to Gray Code Converter. Simulation results of Binary to Gray Code Converter :(b) Input waveform W (b) Input waveform X (c) Input waveform Y (d)Input waveform Z (e) Output waveform A (f) Output waveform A (g) Output waveform B (h)Output waveform C (i) Output waveform D

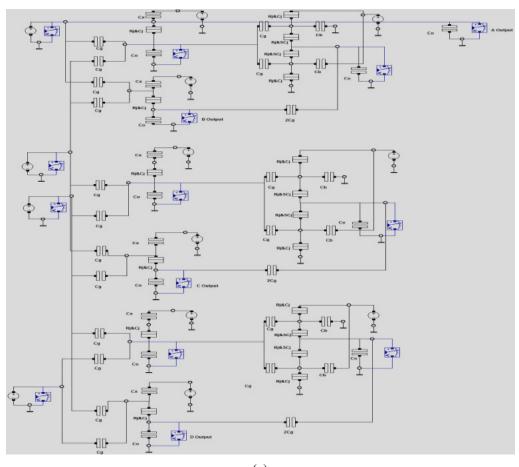

## **5.9 Gray to Binary Code Converter**

This circuit performs the gray to binary code conversion and has been designed using single electron device as shown below.

Figure 14:(a)Single electron device based Gray to Binary Code Converter. Simulation results of Gray to Binary Code Converter: (b)Input waveform W (c) Input waveform W (d) Input waveform W (e) Input waveform W (f) Output waveform W (g) Output waveform W (h) Output waveform W (ii) Output waveform W (b) Output waveform W (c) Input waveform W (d) Input waveform W (e) Input waveform W (f) Output waveform W (g) Ou

## 6. CONCLUSION

In this paper, the design and simulation of novel digital circuits have been presented. The design and simulation has been accomplished using a Monte Carlo based tool for single electron circuit simulation named SIMON 2.0. The outputs of the digital circuits have been verified. The work was started off with the designing of the basic logic gates and its functional attributes were substantiated. This work can be stretched out to build bigger circuits where we can explore the possibility of large scale integration that runs on very low power. Further this work can also be drawn out to design subsystems. Accuracy is assured when using the Monte Carlo method but the process experiences a setback in terms of time efficiency while simulating large circuits.SETs are known to run on very less current and hence exhibits low power dissipation. On the other hand CMOS functions at realistic temperatures. Therefore, SET-CMOS circuits can be fabricated with the help of another MC based simulator called SMARTSPICE offering better accuracy.

## ACKNOWLEDGEMENTS

I am using this opportunity to express my gratitude to everyone who supported me throughout the course of this M.Tech project. I am thankful thanks to **Prof.Dr. P.C Pradhan**, (Professor, Department of Electronics and Communication Engineering, SMIT, Majitar) and **Mr. Amit Agarwal**(Assistant Professor, SMIT, Majitar) for their aspiring direction, invaluably constructive criticism and friendly advice during the project work. I am sincerely grateful to them for sharing their truthful and illuminating views on a number of issues related to the project. I would also like to thank **Prof. (Dr.) R. N. Bera (HOD, E & C Dept., SMIT)**, for granting me the permission to advance with my project and work in my field of interest. I express my sincere thanks and heartfelt gratitude to my parents for their never ending love, support and encouragement which have enabled me to overcome all the hardships all throughout. Lastly, I would like to thank to all my friends for assisting me and offering their selfless help during the course of my project.

## REFERENCES

- 1. Mahima U, Rajanna K.M., Vijaykumar R.H., "Design and simulation of 2-bit comparator using SET Based Logic Circuits," International Journal of Innovative Research in Advanced Engineering, Vol.2, Issue 7, July 2015, ISSN: 2349-2163, pp. 66-70.

- 2. K.K Likharev,"Single electron Devices and their Applications," 0018-9219/99 IEEE, Proceedings of the IEEE, Vol.87, No.4, April 1999.

- 3. "Addition Related Arithmetic Operations via Controlled transport of Charge," IEEE Trans.on Computers, Vol.54, No.3, March 2005.

- 4. Katsuhiko Degawa Takafumi Aoki, Tatsuo Higuchi, Hiroshi Inokawa and Yasuo Takahashi, "A Single- Electron Transistor Logic Gate Family and Its Application Part I:Basic Components for Binary, Multiple- valued and Mixed- mode logic," Proceedings of the 34th International Symposium on Multi-Valued Logic (ISMVL '04) 0195-623X/04.

- 5. Sameh Ebrahim Rehan, "A Novel half adder using SET Technology," Proceedings of the 2nd IEEE International Conference on Nano/Micro Engineered and Molecular Systems, January 16-19,2007, Bangkok, Thailand, 1-4244-0610-2/07.

- 6. G.T. Zardalidis and I. Karafyllidis, "Design and simulation of a single electron full adder," IEEE Proc.- Circuits, Devices and Systems, Vol. 150, No.3, June 2003.

- Costa Gerousis and Arthur Grepiotis, "Programmable Logic Arrays In Single Electron Transistor Technology," ICSES 2008 International Conference On Signals And Electronic Systems Kraków, September 14-17, 2008.

- 8. S. Sahlivahanan, N Suresh Kumar, "Electronic Devices and Circuits," Second edition.

- 9. Module 2: MOSFET, Lecture 7: Advanced Topics.

- Santanu Mahapatra, "Hybrid CMOS Single-Electron-Transistor Device and Circuit Design," Artech House Publication, 2006.

- 11. Masaharu Kirihara and Kenji Taniguchi, "Monte Carlo simulation for single electron circuits," IEEE, 0-7803-3662-3/97.

- 12. Wasshuber, C. Kosina, H. Selberherr S., "SIMON- A Simulator for Single Electronics Devices and Circuits," IEEE, Vol.16, Issue 9, September 1997,pp. 937-944, ISSN0278-0070.

- Amirthalakshmi T.M, Dr. S Selvakumarraja, "The Upcoming VLSI Based Integrated Circuits: A Recent Survey of Nanodevices," International Journal of Advances in Science and Technology, Vol.2, Issue 2, June 2014, pp.55-62, ISSN 2348-5426.

- 14. F. D'Agostino, D Quercia, "Short Channel Effects in MOSFETs," December 11th ,2000.

- 15. Shilpa Goyal, Anu Tonk, "A Review towards Single Electron Transistor (SET)," International Journal of Advanced in Computer and Communication Engineering, Vol.4, Issue 5, May 2015.

- 16. P.C Pradhan, Kushal Pokhrel, S K Sarkar, Amit Agarwal, Sharmistha Chetia, "Design and simulation of SR,D and T Flip Flops modeled with Single Electron Devices," International Symposium on Devices MEMS, Intelligent Systems & Communication, Proceedings published by International Journal of Computer Application, 2011, pp. 16-21.

- 17. Vinay Pratap Singh, Arun Agarwal and Shyam Babu Singh, "Analytical Discussion of Single Electron Transistor (SET)," International Journal of Soft Computing and Engineering, Vol.2, Issue 3, July 2012, ISSN: 2231-2307.

- 18. Dinh Sy Hien, "Some New Results of Quantum Simulator NEMO-VN2," Progress in Nanotechnology and Nanomaterials, Vol.2, Issue 3, pp. 55-63, July 2013.

- 19. Lee Jia Yen, Ahmad Razdi Mat Isa, Karsono Ahmad Dasuki, "Modelling and simulation of single-electron transistors," Journal of Fundamental Sciences, November 2005, pp.1-6.

- 20. Dihn Sy Hien, Huynh Lam Thu Thao and Le Hoang Minh, "Modelling transport in single electron transistor," Workshop on Advanced Materials Science and Nanotechnology, Journal of Physics: Conference Series 187(2009) 012060, doi: 10.1088/1742-6596/187/1/012060.

- 21. Kulik,I.O., and R.I Shekhter,"Kinetic Phenomena and Charge Discreteness Effects in Granular Media," Sov.Phys.-JETP,Vol.41,1975,pp.308-316.

- 22. Averin, D. V., and K. Likharev," Single-Electronics: Correlated Transfer of Single Electrons and Cooper Pairs in Small Tunnel Junctions," in Mesoscopic Phenomenain Solids, B. Altshuler, P. Lee, and R. Webb (Eds.), Amsterdam, The Netherlands: Elsevier, 1991, pp. 173-271.

- 23. Likharev, K., "Single-Electron Devices and Their Applications," Proc IEEE, Vol. 87, No. 4, 1999, pp. 606-632.

- 24. Beenakker, C.W.J., "Theory of Coulomb Blockade Oscillations in the Conductance of a Quantum Dot," Phys.Rev.B, Vol.44, No.4, 1991, pp. 1646-1656.

25. Stephen M. Goodnick and Jonathan Bird, "Quantum-Effect and Single IEEE Trans. on Nanotechnology, vol.2, No. 4, Dec. 2003.

Electron Devices",

- 26. Institute of Microelectronics, www.iue.tuwien.ac.at/index.php?id=simon

- 27. N. Basanta Singh, Sanjoy Deb, Asish Kumar De and Subir Kumar Sarkar, "Design and Simulation of 2–TO-4 Decoder Using Single Electron Tunneling Technology Based Threshold Logic Gate," Journal of Electron Devices, Vol. 9, 2011, pp. 342-351.

- 28. Nicholas Allec, Robert Knobel, Li Shang, "Adaptive Simulation for Single-Electron Devices", 1 March 2008, EDAA.

- 29. E.L. Pankratov, E.A. Bulaeva, "On Prognozisys of Manufacturing Double-Base Heterotransistor and Optimization of Technological Process", Advances in Materials Science and Engineering: An International Journal (MSEJ), Vol. 2, No. 1, March 2015.

- 30. Vivek Kumar, Dr. Prakash Verma,"Design and Fabrication of Planetary Drive Magnet Pedal Power Hub-Dynamo", Advances in Materials Science and Engineering: An International Journal (MSEJ), Vol. 2, No. 3, September 2015.

#### **Authors**

**Banani Talukdar** received my B.Tech Degree in Electronics and Communication Engineering from Don Bosco College of Engineering and Technology, Guwahati, Assam, India. I am currently pursuing my M.Tech Degree in Digital Electronics and Advanced Communication at Sikkim Manipal Institute of Technology, Majitar, Sikkim, India. My interests include working in the field of Digital electronics, nanotechnology and Single electron devices.

**Dr. P.C. Pradhan** received my B.E Degree in Electronics and Communication Engineering from LD College of Engineering. I have completed my M.Tech degree in Digital Electronics and Advanced Communication from Sikkim Manipal Institute of Technology, Majitar, Sikkim, India. I have also obtained my Ph.D Degree in Electron Devices from Jadavpur University, Kolkata, West Bengal, India. I am currently working as a Professor in the Department of Electronics and Communication Engineering at Sikkim Manipal Institute of Technology, Majitar, Sikkim, India.

Amit Agarwal received my B.Tech Degree in Electronics and Communication Engineering from Sikkim Manipal Institute of Technology, Majitar, Sikkim, India. I have also received my M.Tech degree in Digital Electronics and Advanced Communication from Sikkim Manipal Institute of Technology, Majitar, Sikkim, India. Currently pursuing my Ph.D Degree.