# HALF ADDER DESIGN AND SIMULATION USING GRAPHENE NANORIBBONS AND FINFETS

Nishtha Khare<sup>1</sup>, Vangmayee Sharda<sup>2</sup> and Anushree<sup>1</sup>

$^1\mathrm{Hindustan}$  college of science & technology , Farah, Mathura (U.P), India  $^2\mathrm{Amity}$  University , Uttar Pradesh, India

## **ABSTRACT**

In combinational logic circuits, half adder plays an important role in computation of arithmetic units. As far as digital electronics is concerned, high processing adders have significant contribution in total delay and power of the system. This paper presents the comparison between the rise time and fall time obtained at the sum and carry outputs of the half adder deigned by the using simple interconnects, designed by using graphene nanoribbon (GNR) interconnects and also the half adders simulated using FinFET drivers and GNR interconnects.

#### KEYWORDS-

Half adders, Graphene Nanoribbon interconnects, FinFETs, MLGNR, SLGNR, Rise time and Fall time.

# 1. Introduction

According to Moore's law the number of transistors in an Integrated circuit (IC) is expected to double every year. This means that to accommodate a large number of transistors on a single IC, the dimensions of the transistors should be reduced. Also in order to perform at par with these transistors at such nano-scale regime, the interconnects used for designing of the circuit should also be downscaled. Thus a need to design the interconnects at the nano-scale technology has evolved with the recent advancements in the field of VLSI [1].

In most of the VLSI circuits, copper (Cu) interconnects are used as the interconnect technology. When these Cu interconnects are used at the nano-scale regime, they get affected by sidewall scattering and grain boundaries [2]. In order to overcome the problems raised due to copper interconnects, other feasible solutions for global interconnects where researched. One such solution emerged as Graphene nanoribbon interconnects (GNRs). The GNRs are fabricated by etching and patterning of Graphene which has the most promising properties including large mean free paths, high current densities and thermal conductivity [3].

#### 2. TECHNOLOGIES USED

#### 2.1 Interconnect technology: Graphene Nanoribbons

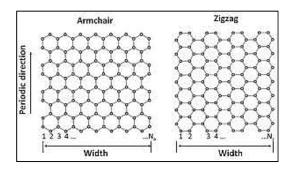

Graphene is a zero-gap material represented by carbon atoms arranged in a honey-comb structure [4]. The unzipping of carbon nanotubes and pattering of graphene both results in construction of graphene nanoribbons (GNRs). These ribbon like strips of graphene have dimensions less than 10nm [5]. Depending on their geometry the GNRs are classified as metallic or semiconducting. Also depending on their band structures, GNRs can be divided into zig-zag GNRs and armchair GNRs as shown in Figure 1. The zig-zag GNRs are always metallic in nature while armchair GNRs can be either metallic or semiconducting [6].

Futher GNRs can be classified based on the number of layers present, they can be SLGNRs (Single layer graphene nanoribbons) and MLGNRs (Multi-layer graphene nanoribbons) [7].

Figure 1. Armchair and zigzag GNRs

# 2.2 Driver technology: FinFET

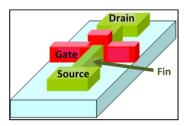

FinFET is a multi-gate metal oxide semiconductor field effect transistor (MOSFET). The design of a FinFET includes a conducting channel that rises above the insulator level and creates a structure of a thin silicon, that is shaped like a fin (Figure 2). Due to this fin, number of gates can operate with a single transistor.

Figure 2. FinFET structure

The main advantages of using FinFET technology include reduction in short channel effects, sharper contrast between on/off states and also reduction in leakage. Usage of FinFETs provide faster switching speeds and also low power consumption [8].

Intel also designed FinFET in 2012 for its commercial use. The shape of Intel's FinFET is in the form of a triangle unlike rectangle as in usual FinFETs. The logic behind is, that a triangle has a higher structural strength as compared to a rectangle [9].

## 3. RLC MODEL FOR GNR INTERCONNECTS

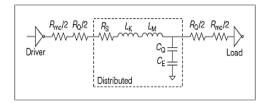

Figure 3. RLC model representation for GNRs

The Figure 3 represents the RLC model for GNR interconnects [10].

# $R_{O}$ (Quantum contact resistance):

$$((\hbar / 2e^2) / N_{ch} . N_{layer}) = 12.94 \text{ K}\Omega/N_{ch}.N_{layer}$$

(1)

#### C<sub>0</sub> (Quantum capacitance):

$$N_{ch}$$

.  $N_{layer}$ .  $4e^2 / \hbar V_f$ ) aF/ $\mu$ m (2)

$$C_{E}$$

(electrostatic capacitance):

$$E_0 *(w/d) aF/\mu m$$

(3)

## **I**<sub>K</sub> (Kinetic Inductance):

$$(\hbar/4e^2 V_f)/N_{ch}.N_{layer} nH/\mu m$$

(4)

## **I**<sub>M</sub> (magnetic Inductance):

$$\mu_{0}*(d/w) nH/\mu m \tag{5}$$

#### Where

$\hbar$  = Planck's constant (6.626 x 10<sup>-34</sup> J.s)

e = Electronic charge  $(1.6 \times 10^{-19} \text{ C})$

N<sub>ch</sub> = Number of conducting channels in one layer

$N_{layer}$  = Number of GNR layers

$V_f$  = Fermi velocity =  $8*10^5$  m/s for GNR

w = width of MLGNR

d = distance from the ground.

$\xi_0 = 8.85 * 10^{-12}$  (Electrostatic Permittivity)

$\mu_0 = 4\Pi * 10^{-7} (Magnetic Permeability)$

$$N_{ch} = N_{ch,electron} + N_{ch,hole} N_{ch}$$

$$= \sum [1 + \exp((E_{n,\text{electron}} - E_F)/k_B T)]^{-1} + \sum [1 + \exp((E_F - E_{n,\text{hole}}) / k_B T)]^{-1}$$

(6)

Where  $E_{n, \text{ electron}}(E_{n, \text{ hole}}) = \text{minimum (maximum) energy of the } n^{\text{th}}$  conduction (valence) subband.

## 4. SIMULATION SETUP

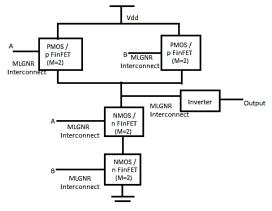

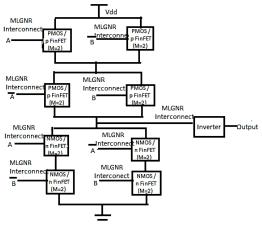

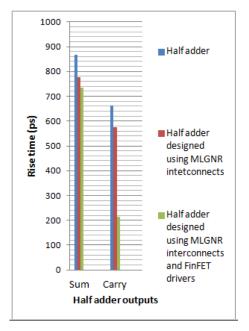

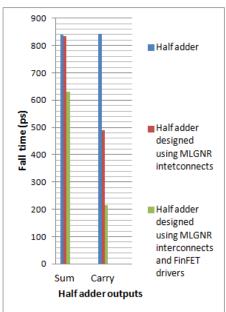

In this paper Half adder circuit is first designed using normal interconnects and the rise time and fall time obtained at the outputs of the sum and carry are observed. Secondly, the same half adder circuit is redesigned using MLGNR interconnects and the difference in the outputs of the first case and second case is compared. In the last circuit of half adder the FinFET drivers are used with MLGNR interconnects. The results obtained from all the three circuit are compared and analysed.

The parasitic values for the MLGNR interconnect are calculated on the basis of the RLC model (Fig.1.3) designed and discussed in the previous section (section 3). For the purpose of calculation of RLC parameters, equations (1), (2), (3), (4) and (5) are used with the following assumptions:

$N_{layer}(Number of MLGNR \ layers) = 10$ Total number of conducting channels in one layer = 1 d (distance from the ground) = 50 nm w (width of MLGNR) = 10 nm l (length of MLGNR) = 10  $\mu$ m Number of Fins(M) in FinFET drivers = 2

All the simulations in this paper are performed at 16 nm scale on TSPICE software using Predictive Technology models of BSIM-CMG by BSIM group at University of California, Berkeley.

# 5. HALF ADDER

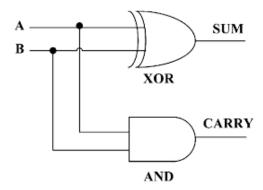

Figure 4. Logic circuit diagram for half adder

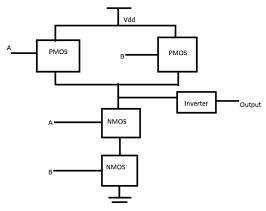

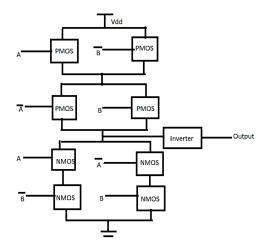

The half adder circuit is designed (Figure 4) using XOR and AND logic gates which provide the Sum and the carry outputs respectively [11].

| A | В | Sum | Carry |

|---|---|-----|-------|

| 0 | 0 | 0   | 0     |

| 0 | 1 | 1   | 0     |

| 1 | 0 | 1   | 0     |

| 1 | 1 | 0   | 1     |

Table 1.1 Truth table for half adder

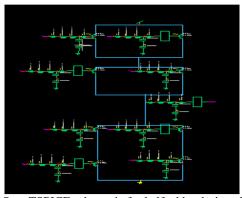

Figure 5. AND gate schematic for half adder circuit, that provides carry as the output

International Journal of Modelling, Simulation and Applications (IJMSA) Vol.1, No. 1

Figure 6. XOR gate schematic for half adder, the output of this gate is provided as the sum of the inputs

Figure 7. AND gate schematic designed using 5 MLGNR interconnects / FinFET drivers

Figure 8. XOR gate schematic designed using 9 MLGNR interconnects / FinFET drivers

Carry TSPICE schematic for half adder designed using MLGNRs / FinFETs

Figure 9

Sum TSPICE schematic for simple half adder

Sum TSPICE schematic for half adder designed using MLGNRs / FinFETs

Figure 10

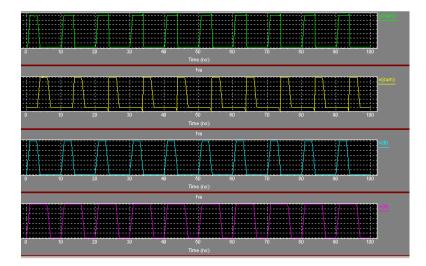

Figure 11. Sum and carry output waveform for half adder

## International Journal of Modelling, Simulation and Applications (IJMSA) Vol.1, No. 1

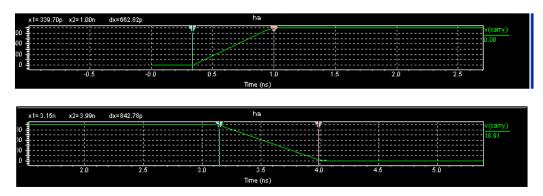

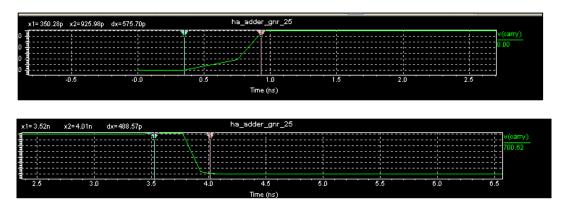

Figure 12. Carry rise time and fall time for simple half adder

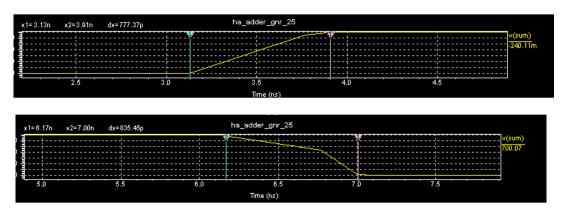

Figure 13. Sum rise time and fall time in case of simple half adder

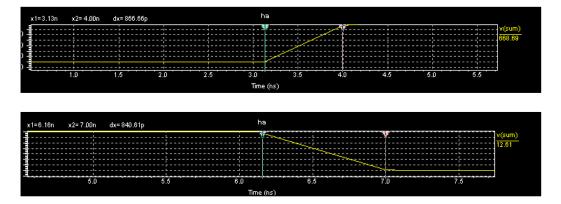

Figure 14. Carry rise time and fall time for half adder designed using MLGNR interconnects

Figure 15. Sum rise time and fall time for half adder using MLGNR interconnects

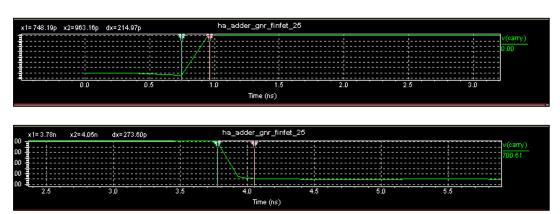

Figure 16. Carry rise time and fall time for half adder designed using FinFETs and MLGNR interconnects

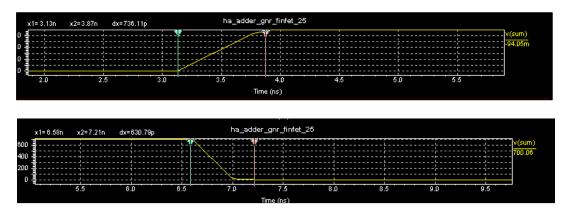

Figure 17. Sum rise time and fall time for half adder designed using FInFETs and MLGNR interconnects

| Table 1.2 Su | im and carry rise | time and fall tim | e for a half adder |

|--------------|-------------------|-------------------|--------------------|

|              |                   |                   |                    |

|                         | Half Adder | Half adder designed using MLGNR interconnects | Half adder designed using FinFETs and MLGNR |

|-------------------------|------------|-----------------------------------------------|---------------------------------------------|

|                         |            |                                               | interconnects                               |

| Rise time<br>(Sum)      | 866.66 ps  | 777.37 ps                                     | 736.11 ps                                   |

| Fall time (Sum)         | 840.61 ps  | 835.45 ps                                     | 630.79 ps                                   |

| Rise<br>time<br>(Carry) | 662.82 ps  | 575.70 ps                                     | 214.97 ps                                   |

| Fall time<br>(Carry)    | 842.78 ps  | 488.57 ps                                     | 273.60 ps                                   |

The above Table 1.2 shows the values of rise time and fall time obtained in all the three differently designed half adder circuits. The variation in the timings clearly show that with the incorporation of MLGNR interconnects in the half adder circuit, both the rise time and fall time are decreased. Furthermore by using FinFET drivers with GNR interconnects, a much reduction in rise and fall times is observed.

Table 1.3 Percentage improvement comparison for both rise and fall time at sum and carry

| % improvement in the rise time and fall time |               |               |               |  |

|----------------------------------------------|---------------|---------------|---------------|--|

|                                              | Between       | Between       | Between       |  |

|                                              | Half adder &  | Half adder &  | Half adder    |  |

|                                              | Half adder    | Half adder    | with          |  |

|                                              | designed      | designed      | MLGNR         |  |

|                                              | using         | using         | interconnects |  |

|                                              | MLGNR         | FinFETs and   | and Half      |  |

|                                              | interconnects | MLGNR         | adder         |  |

|                                              |               | interconnects | designed      |  |

|                                              |               |               | using         |  |

|                                              |               |               | FinFETs and   |  |

|                                              |               |               | MLGNR         |  |

|                                              |               |               | interconnects |  |

| Rise time                                    | 10.30         | 10.02         | 5.30          |  |

| (Sum)                                        |               |               |               |  |

| Fall time                                    | 0.61          | 24.96         | 24.49         |  |

| (Sum)                                        |               |               |               |  |

| Rise time                                    | 13.14         | 67.56         | 62.65         |  |

| (Carry)                                      |               |               |               |  |

| Fall time                                    | 42.02         | 67.53         | 43.99         |  |

| (Carry)                                      |               |               |               |  |

The percentage improvement in the rise and fall time can be understood from the above table 1.2. It is clear that if Graphene Nanoribbons and FinFETs are incorporated with the half adder circuit, an appreciable amount of reduction in the timings can be obtained.

## 6. RESULTS AND DISCUSSIONS

In this paper a study on half adder circuit is performed. The sum and carry outputs of the half adder are analysed on the basis of their rise time and fall time. The study is enhanced by modifying the same circuit with MLGNR interconnects and further by including FinFET drivers as well. The number of multi layer graphene nanoribbon interconnects (MLGNRs) and the

number of fins in finFET drivers can be increased or decreased according to the requirement of the designer. The embodiment of these technologies in the half adder circuit produced refined results as compared to the results obtained using a simple half adder circuit.

On an average the percentage improvement in the sum output of the circuit is 12.61% similarly in the carry output the average percentage improvement obtained is 49.48%.

Graph 1. The rise time and fall time distribution between the three half adder circuits designed in the paper.

#### 7. CONCLUSION

The simulations performed on TSPICE, have evidently shown that Graphene nanoribbons are suitable candidate for the interconnects in digital circuits like half adder. Also, by replacing the traditional CMOS drivers with FinFET drivers has contributed in achieving a gradual decrease in the timings. A much profound study on both of these new technologies may result in obtaining prudent results in the field of VLSI.

# **ACKNOWLEDGEMENTS**

The author would like to thank family, friends and Hindustan College of Science & Technology, Farah, Mathura for their continuous support throughout the research. A special thanks to Dr. Vangmayee Sharda and Ms. Anushree for providing valuable guidance in completing the research work.

## REFERENCES

- [1] A. Ceyhan and A. Naeemi, "Interconnect issues: history and future prospects, part 2," Futurefab Intl., A thought leadership project from MazikMedia, Inc.,issue46, 7<sup>th</sup> April. 2013.

- [2] R.Murali, K. Brenner, Y.Yang, T.Becj, and J. D. Meindi, "Resistivity of Graphene Nanoribbon interconnects," IEEE Electron Device Letters, pp.611-613, vol.30, no.6, June 2009.

- [3] N. Reddy K., M.K. Majumdar, B.K. Kaushik, S.K. Manhas and B. Anand, "Dynamic crosstalk effect in multilayer graphenenanoribbon interconnects," 2012 International conference on communication, devices and intelligent systems (CODIS), pp.472-475, 28-29 Dec.2012.

- [4] S. Saxena and T. A. Tyson, "Ab initio density functional studies of the restructuring of graphene nanoribbons to form tailored, single walled carbon nanotubes," carbon, vol.48, no.4, pp.1153-1158, Apr.2010.

- [5] S. Duttaa and S.K. Pti, "Novel properties of graphene nanoribbons: a review," feature article, Journal of Materials Chemistry, pp. 8207-8223, 29 June 2010.

- [6] S. Rakheja, V. Kumar, and A. Naeemi, "Evaluation of the potential performance of graphene nano-ribbons as on-chip interconnects," contributed paper, proceedings of IEEE, vol. 101, no.7, pp. 1740-1765, July 2013.

- [7] Y. Wu, P. A. Childs, "Conductance of Graphene Nanoribbon Junctions and the Tight Binding Model," Nano scale research letters, vol.6,2011.

- [8] D. Pribat and Y.H.Lee, "Carbon nanotubes and graphene for various applications in electronics: competition and synergy," IEEE technology Time Machine symposium on Technologies Beyond 2020 (TTM), pp.1-2, 1-3 June 2011.

- [9] http://en.wikipedia.org/wiki/Multigate\_device#FinFET.

- [10] Vangmayee Sharda, R.P. Agarwal, "MLGNR interconnects with FinFET driver: Optimized delay and power performance for technology beyond 16nm", International Journal of Research in Engineering and Technology, eISSN: 2319-1163, pISSN: 2321-7308.

- [11] http://www.elprocus.com/half-adder-and-full-adder.

#### Authors

Nishtha Khare has completed B.tech (Electronics & Telecommunications) in 2012 from Amity University, Noida (U.P.). She has worked with Wipro technologies for 2 years (2012-14) in the field of testing. She is currently pursuing her M.tech (VLSI Design) from Hindustan College of Science & Technology. Her research study work is involved in the field of VLSI interconnects, CNTs and GNRs.

Vangmayee Sharda has completed her Ph.D. in 2016 in GNR interconnects from Shobhit University (U.P). She has done M.Tech (VLSI) in 2011 from Shobhit University, Meerut. She has worked with BARC for 2 years (2006- 2008) in the field of ASIC Designing. She is currently working at Amity University, Noida, as Assistant Professor since 2009. Her research interests are interconnects, ASIC designing and sub-micron VLSI.

Anushree has completed her B.Tech in Electronics & Communication and M.tech (VLSI Design) from Hindustan College of Science & Technology. She has an experience of 4.5 years in the field of teaching and is currently working as Assistant Professor in Hindustan College of Science & Technology.