# OVERCURRENT RELAY COORDINATION IN DISTRIBUTED GENERATION WITH FAULT CURRENT LIMITER

## Amit A. Chatte

Department Of Electrical Engineering, Yeshvantrao Chavan College of Engineering, Nagpur, Maharashtra, India

### **ABSTRACT**

The distribution network has many advantages when it is connected to distributed generation (DG). Some problems in coordination of protection devices will occur in the presence of DG, due to change in short circuit level at different points. Fault current limiter (FCL) is applying limit to the fault current levels and the effect of DGs on coordination of overcurrent (O/C) relay during the faults. In distribution network the use of FCL & DG causes some transient current during fault condition. In such network steady state coordination method do not result inaccurately. In this method we use fault current limiter for reducing the transient fault current in the network. The method gives feasible and effective solutions for optimal coordination in the practical power system networks in comparison to the previous steady state methods when simulations are carried out on a sample network and the results are demonstrated.

## KEYWORDS

Distributed generation (DG), fault current limiter (FCL), overcurrent, relay coordination, distribution system.

## 1. Introduction

Distribution network has many advantages [1] when it is connected to distributed generation (DG). Due to changes in direction and value of power flow (under normal operation) and short circuit current level in different points (under fault conditions) some problems in coordination of protection devices will occur. Location, size and technology type of DG depends on the impact of DG [2] on protective coordination. To overcome the overcurrent (O/C) relay coordination problem in power systems with DGs several ideas have been introduce. In [3-6], when a new DG is connected the effect of DG on the short circuit current level is suggested and surveyed for the checking of protective relay coordination each time. As a proper solution to the problem of fuserecloser coordination in the system with DG is suggested that is the use of microprocessor based recloser [4]. All downstream DGs of the recloser before a recloser action are disconnected to prevent DG reconnection without synchronism. However, this will lead to synchronization problems for reconnecting DGs into the network after clearing the fault and lose of DG power. An adaptive protection scheme is proposed [5] to achieve fuse relay coordination in the distribution system with high penetration of DGs to prevent disconnecting of all downstream DGs. This solution may technically work, to replace the existing relays with microprocessor based relays involve very high initial equipment cost and to implement special breakers and a substation computer to control this breakers. They are not applicable for existing distribution system today because of these complications and high cost [7]. In [7] to limit the effect of DG on coordination of the O/C fault current limiter (FCL) is used. To limit the fault current to an acceptable level during fault and to gives very low impedance and power loss under normal operations FCL is a device which is connected in series with DG. [8]. Different types of FCL DOI: 10.5121/eeij.2017.4101

schemes are proposed by many research groups. Three main types of FCLs can be identified according to technology used: (a) superconducting fault current limiters (SFCLs), (b) magnetic fault current limiters (MFCLs) and (c) solid-state FCLs [9]. In comparison to SFCL and MFCL, solid state FCL has many advantages. The switching loses are a major problem between them. In [10] by a combination of gate turn-off (GTO) bridges and fast mechanical switch that is suitable for this application a novel hybrid FCL is proposed. To limit the effect of distributed generation (DG) a method for calculation of FCL impedance is presented in [2]. To restore the over current relay coordination the sizes of FCL are determine without a need to change the relay setting or DG disconnection during the fault. However FCL and DG on overcurrent relay coordination has not been surveyed by the impact of transient behaviour. In past to coordinate different types of overcurrent relays with inverse time current characteristics many attempts have been made. The optimal coordination of O/C relays are commonly performed by linear programming techniques, including the simplex, two phase simplex and dual simplex methods by owing the complexity and limitations of traditional methods. The discrimination times ( $\Delta t$ ) of primary and backup relays are considered as constraints in optimization method. For coordination procedure all previous methods use the steady-state fault current in relay equations.

Therefore the solutions of coordination are approximate values. In overcurrent relay coordination's the transient fault current of the network are used in this paper. Because of this reason a real model of hybrid FCL with performance time delay is considered and a dynamic model is applied for relays.

# 2. PROBLEM STATEMENT

The coordination of relays is lost and the use of FCL is one of the effective solutions in restoring the O/C relays coordination in the presence of DG. The detailed description of these problems is given below:

- a. In [2] to maintain coordination of O/C relays after installing DGs many methods are proposed to determine the size of fault current limiter (FCL). In previous studies, dynamic behaviour like performance delay time and switching effects of FCL have not been included. Some miscoordinations of Primary & backup relays because of this transient effect which may causes to pass high value of fault current through overcurrent relay. Before operation of FCL the extra fault currents may also result in a relay trip. Before operation of FCL the extra fault currents may also results in a relay trip transient current of DGs is the another subject that is not considered is the previous studies. The network & influence of the O/C relays coordination, DGs also inject transient and subtransient fault current that contribute in transient behaviour.

- b. In previous studies such as [11], for O/C relays coordination many methods are developed. In calculations of operating time of relays and obtaining the setting of relays the steady state fault current is used. When the fault currents of the network are smooth or the transient components of fault currents are smooth or the transient components of can solve the relay coordination problem using dynamic model of relay in transient condition of the network for obtaining accurate relay settings.

# 3. TRANSIENT BEHAVIOUR OF FCL & DG

As mentioned in section 1, solid state FCL has switching loss due to the use of solid state devices. Mechanical breaker and switches exist that have virtually no closed circuit losses therefore, they can operate quickly and are unable to commutate the voltage across their contacts. Therefore, to solve these problems a novel hybrid FCL is proposed. The mechanical switch is passing the

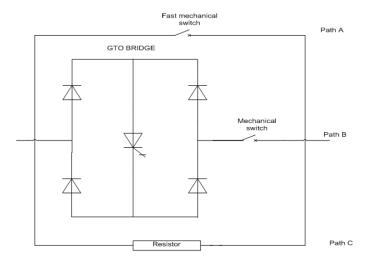

current with no loss and during fault condition the solid state switch operates to commutate and solve the arcing problem during the steady state operation [7]. The circuit of hybrid FCL is shown in Fig (1). The hybrid FCL consists of these parallel path which are path A, path B, and path C. path A includes a fast mechanical switch which commutates the current onto path B. path B includes power semiconductor elements. In path C for fault current limitation this path that is path B forces the current onto resistor element.

Figure 1. Single phase diagram of hybrid fault current limiter

The fast mechanical switch of path A is closed and the GTO switches of path B are gated at the prefault condition. Almost all of the current flows through path A since the resistance of the fast mechanical switch is much smaller than semiconductor switches. It takes 40 ms to detect the fault by fault detection unit when a fault occurs. The fast mechanical switch produces on are voltage drop of about 40 V and opens within 150 ms. The current starts to commutates from path A onto path B [10] when the voltage drop across the semiconductor switches is typically 10-15 V, which is lower than arc voltage.

The GTO switch is turned off after 150 ms to transfer the current to path C when the commutation is completely done. When the fault current flows through the path C the fault current is limited by flowing through the impedance of path C. The mechanical switch in path B is opened when the current reaches zero. To isolate the semiconductor switches from the high transient recovery voltage. For studying the behaviour of hybrid FCL it is modelled in MATLAB Fig 2.

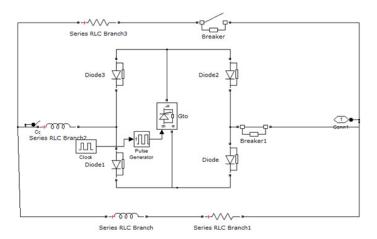

Figure 2. Hybrid fault current limiter model in MATLAB

A variable resistor (R\_arc) is considered in series with an ideal breaker in path A for modelling the arc voltage of the fast mechanical switch. The ideal breaker is close and the resistance value of R\_arc is increased linearly with slope of 200 V per second to model the arc voltage drop (40 V) until complete opening time of SW 1 (150 ms) [10] when the ideal breaker starts to open in fault condition.

The self-inductance in loop A-B & B-c is modelled with two inductors L1 & L2 to consider the actual model of FCL. The self-inductance of the loop A-B must be sufficiently low on the order of L1 = 0.5 mH, to ensure complete current commutation within a short time interval. Also, turning off the GTO causes a very high (di/dt) & the self inductance of the loop B-C on the order of L2 = 10 mH[10] due to an excessive voltage rise in parallel with GTO bridge R the high rise of voltage is limited by metal – oxide varistor. To limit the value of fault current to the level of load current value fault current limiter (FCL) is assumed to be the 15 V.

During fault condition DGs also show transient behaviour. In this paper the type of DG is assumed to be synchronous generator the injected fault current from these DGs, have three states that is sub- transient, transient and steady state. The fault current of DG is obtained by (1)

$$iac(t) = \sqrt{2}Eg\left[\left(\frac{1}{X''d} - \frac{1}{X'd}\right)e^{\left(\frac{-t}{T''d}\right)} + \left(\frac{1}{X'd} - \frac{1}{Xd}\right)e^{\left(\frac{-t}{T'd}\right)} + \frac{1}{Xd}\right]\sin(\omega t + \alpha) \tag{1}$$

DC component of fault current which appears at the instant of fault occurrence is shown as (2)

$$idc(t) = \frac{Eg}{\sqrt{2}} \left[ \left( \frac{1}{X''d} + \frac{1}{X'd} \right) e^{\left( \frac{-t}{Td} \right)} \right] \cos \alpha \tag{2}$$

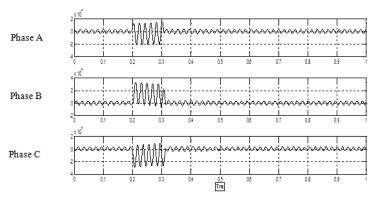

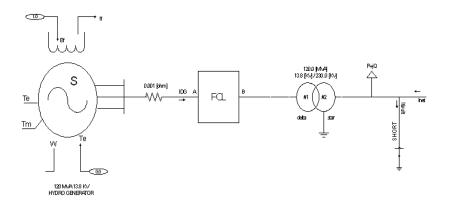

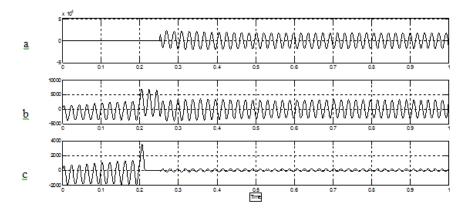

By summation of AC and DC components of the fault current total fault current is obtained. By using the dynamic parameter of (1) & (2) transient fault current are obtained by simulation in MATLAB. A simple network is considered as shown in Fig 4 to evaluate these transient effects of DG & FCL on the fault current. In Fig 3 for three phases the DG fault current without FCL are shown. In these fig, the sub-transient, transient & DC component of each phase differs from the other phases because of the phase difference between the three phases. The DC component is negligible and the sub-transient and transient components can be clearly seen in fault current of

Figure 3. Transient fault current of DG for 3 phase (in ampere)

The FCL is modelled as shown in Fig. 2.in Fig 5 the voltage across the FCL & the fault current passing through FCL is shown in Fig. to consider the DC effect in this simulation it is assumed that the fault occurs at the instant in which the fault current is not zero such as 0.5036s. To detect the fault it takes 40 ms for FCL and they switch SW1 start to open. The voltage across the FCL is shown in Fig 5(a). When the switches of path A and B open to commutate the fault current to path C, it is observed that the voltage rises. Because of high changes in the current of self inductor in path B and C leads to high L(di/dt) at this instant, a jump in voltage appear.

Figure 4. Typical simple network with FCL & DG

Figure 5. Simulation waveform of FCL in transients a. voltage across FCL b. current of FCL c. current passing through fast mechanical switch of FCL

The voltage across the FCL becomes the voltage drop across R\_FCL, when the switches open completely and transfer current to R\_FCL as seen in Fig 5(a). In Fig 5(b) it shows the FCL current and its limitation when the FCL operate. The current is commutated from path A to path B when switch SW1 starts to open and finally the current SW1 becomes zero. The current of commutation is illustrated in Fig 5(c). All the simulation work is carried out in MATLAB 2012a.

## 4. RESULT & DISCUSSION

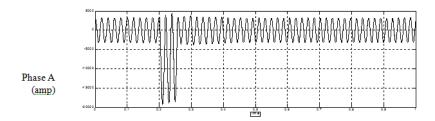

There is a delay time in performance of FCL in actual condition to limit the fault current. Detection time and operation time of FCL switches is delayed due to fault. As shown in Fig 6, before complete operation of FCL for fault current limitation the high DG fault current flows through networks and over current relays for a few cycles. The transient behaviour of FCL and DG should be considered in O/C relays coordination in actual calculations because this subject influences the operation of O/C relays. In phase A, the DG fault current with FCL is shown in Fig 6. As can be seen the FCL limits an acceptable range of current to the DG fault current during the fault condition

Figure 6. Transient fault current limitation of DG by FCL

# 5. CONCLUSIONS

The fault current levels are changed and may lead to miscoordinations in O/C protection by installing DG in power distribution network. In the presence of DG without changes in relay settings FCL is used for restoration of O/C relays coordination. The fault current affects the transient behaviour of DG and FCL. These operation delay time of FCL and transient fault current can disturb the coordination of relays and should be considered in the calculation of relay setting. The dynamic models of DG and FCL are simulated for obtaining the transient fault current. The efficiency of proposed method is finally demonstrated by the results of typical network with those obtained using the steady state coordination method. Results are compared with previous method and new method and the transient fault current of DG is minimized by applying the FCL.

## REFERENCES

- [1] Barker, P., Demello, R.W.: "Determining The Impact Of Distributed Generation On Power Systems: Part 1radial Power Systems". Proc. Ieee Power Engineering Society Summer Power Meeting, 2000, Pp. 1645–1658

- [2] El-Khattam, W., Sidhu, T.S.: "Restoration Of Directional Overcurrent Relay Coordination In Distributed Generation Systems Utilizing Fault Current Limiter", Ieee Trans. Power Deliv., 2008, 23, (2), Pp. 576–585

- [3] Hadjsaid, N., Canard, J.F., Dumas, F.: "Dispersed Generation Impact On Distribution Networks", Ieee Comput. Appl. Power, 1999, 12, (2), Pp. 22–28

- [4] Brahma, S.M., Girgis, A.A.: "Microprocessor-Based Reclosing To Coordinate Fuse And Recloser In A System With High Penetration Of Distributed Generation". Proc. Ieee Power Engineering Society Winter Meeting, 2002 Pp 1645-1658

- [5] Brahma, S.M., Girgis, A.A.: "Development Of Adaptive Protection Scheme For Distribution Systems With High Penetration Of Distributed Generation", Ieee Trans. Power Deliv., 2004, 19, (1), Pp. 56–63

- [6] Girgis, A., Brahma, S.M.: "Effect Of Distributed Generation On Protective Device Coordination In Distribution System". Proc. Large Engineering Systems Conf. On Power Engineering, July 2001, Pp. 115–119

- [7] Tang, G., Iravani, M.R.: "Application Of A Fault Current Limiter To Minimize Distributed Generation Impact On Coordinated Relay Protection". Presented At The Int. Conf. Power Systems Transients, Montreal, Qc, Canada, 19–23 June 2005

- [8] Paul, W., Rhyner, J., Platter, F.: "Superconducting Fault Current Limiters Based On High Tc Superconductors". Iee Colloquium Fault Current Limiters A Look At Tomorrow, 1995, Pp. 4/1–4/4

- [9] Kumara, J.R.S.S., Atputharajah, A., Ekanayake, J.B., Mumford, F.J.: "Over Current Protection Coordination Of Distribution Networks With Fault Current Limiters". Ieee Conf., Montreal, Quebec, 2006

- [10] Steurer, M., Fro Hlich, K., Holaus, W., Kaltenegger, K.: "A Novel Hybrid Current-Limiting Circuit Breaker For Medium Voltage: Principle And Test Results", Ieee Trans. Power Deliv., 2003, 18, (2), Pp. 460–467

- [11] So, C.W., Li, K.K.: "Time Coordination Method For Power System Protection By Evolutionary Algorithm", Ieee Trans. Ind. Appl., 2000, 36, (5), Pp. 1235–1240

#### **AUTHORS**

**Amit A. Chatte** was born in 26<sup>th</sup> August 1993 in Nagpur, India. He received the B.E Degree in Electrical Engineering from RTMNU Nagpur University. He is now pursuing his M.Tech (Integra ted power system) Degree from YCCE Nagpur affiliated by RTMNU NagpurUniversity.